SMART: Scalable Modular Architecture for RF Transceivers

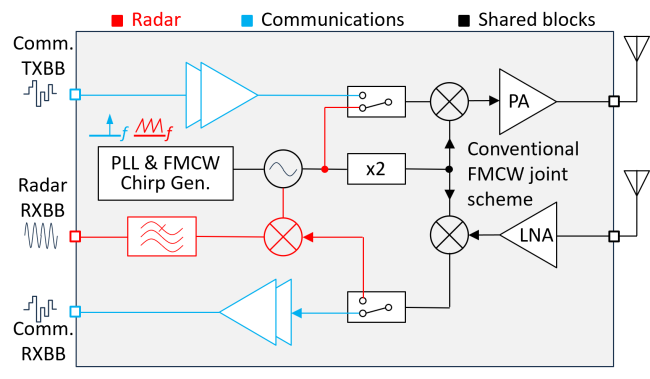

State of the Art of Integrated Sensing and Communication (ISAC) Architecture

A Single Transceiver for Integrated Sensing and Communication

As part of the CHIPS for America funded Microelectronics Commons initiative, Alphacore is developing Scalable Modular Architecture for RF Transceivers (SMART) with multi-channel and multi-band communication, beamforming, and sensing capabilities to realize this vision.

Through Arizona State University’s Southwest Advanced Prototype (SWAP) HUB, and alongside partners at Rice University, Auburn University and Lockheed Martin Corporation, Alphacore is advancing radio frequency transceiver technology to improve national defense and commercial capabilities.

Integrating communications and sensing in a single system-on-a-chip increases resource efficiency, optimizes spectrum utilization, reduces latency and improves reliability while reducing the size and cost of transceivers. The goal of the project is to create a transceiver integrated on a single microelectronics chip, capable of both communications and sensing functions with novel capabilities for devices using 5G and 6G mobile networks and beyond.

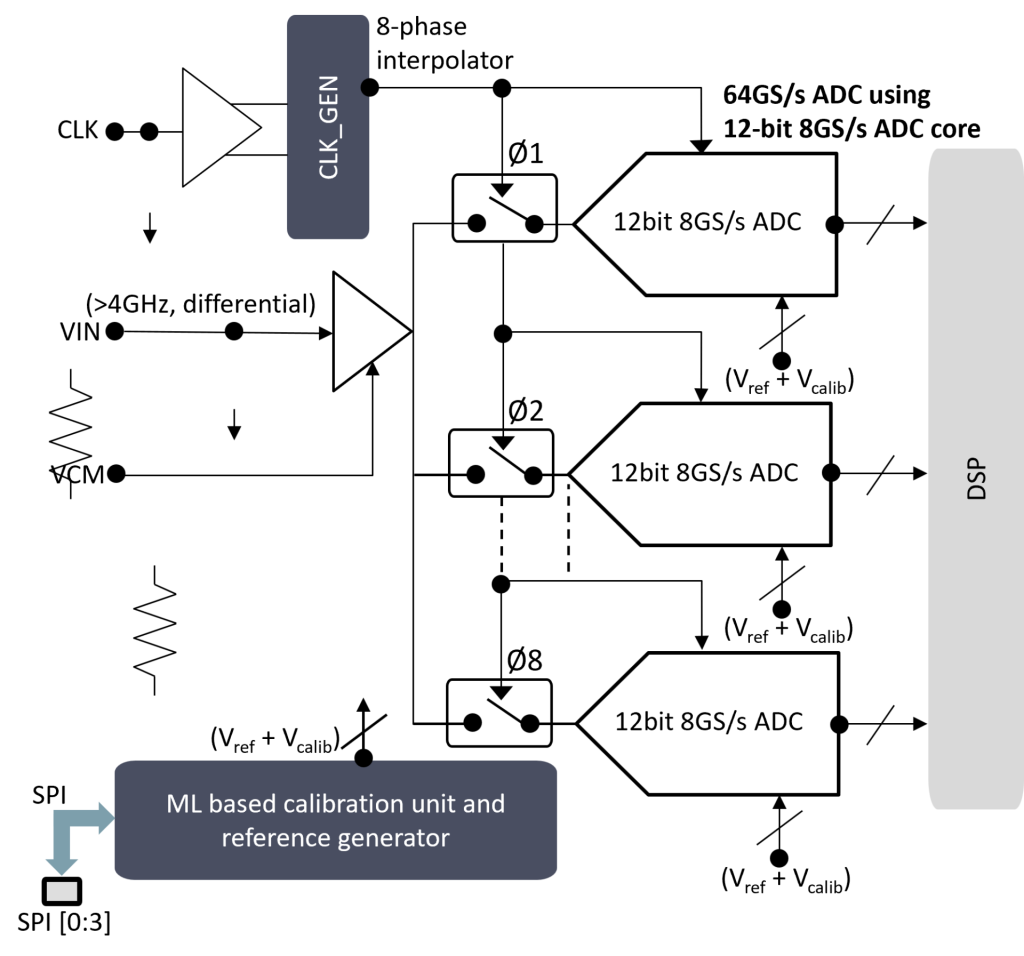

Proposed 64 GS/s ADC and DAC cores

The end result of this program will result in a 64 GS/s analog-to-digital converter an digital-to-analog converter, leveraging Alphacore’s silicon proven RF data converters.

For example, here is a high-level block diagram of how 64 GS/s will be achieved using our 12-bit 8 GS/s ADCs and time interleaving them.

Using Alphacore’s machine-learning based spur calibration technology, our ADCs have low-power and high speeds, with wide instantanous bandwidths and effective number of bits.

Using Alphacore’s machine-learning based spur calibration technology, our ADCs have low-power and high speeds, with wide instantanous bandwidths and effective number of bits.